题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

已知某计算机控制系统中RAM容量为4K×8位,首地址为0x4800,则其最后一个单元的地址为多少(要求给出计算过程)?

如果结果不匹配,请 联系老师 获取答案

如果结果不匹配,请 联系老师 获取答案

题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

如果结果不匹配,请 联系老师 获取答案

如果结果不匹配,请 联系老师 获取答案

更多“已知某计算机控制系统中RAM容量为4K×8位,首地址为0x4…”相关的问题

更多“已知某计算机控制系统中RAM容量为4K×8位,首地址为0x4…”相关的问题

某计算机主存容量为64KB,其中ROM区为4KB,其余为RAM区,按字节编址。现要用2K×8位的ROM芯片和4K×4位的RAM芯片来设计该存储器,则需要上述规格的ROM芯片数和RAM芯片数分别是()。

A.1、15

B.2、15

C.1、30

D.2、30

某计算机的主存地址空间中,从地址0000H~3FFFH为ROM存储区域,从地址

4000H~7FFFH为RAM的存储区域。RAM的控制信号为CS和WE,CPU的地址线为A15~A0,数据线为8位的D7~D0线,控制信号有读写控制R/W和访存请求MREQ,要求: (1)画出地址译码方案。 (2)如果ROM和RAM存储器芯片都采用8 K×1位的芯片,试画出存储器与CPU的连接图。 (3)如果ROM存储器芯片采用8K×8位的芯片,RAM存储器芯片采用4K×8位的芯片, 试画出存储器与CPU的连接图。 (4)如果ROM存储器芯片采用16K×8位的芯片,RAM存储器芯片采用8K×8位的芯片,试画出存储器与CPU的连接图。

4000H~7FFFH为RAM的存储区域。RAM的控制信号为CS和WE,CPU的地址线为A15~A0,数据线为8位的D7~D0线,控制信号有读写控制R/W和访存请求MREQ,要求: (1)画出地址译码方案。 (2)如果ROM和RAM存储器芯片都采用8 K×1位的芯片,试画出存储器与CPU的连接图。 (3)如果ROM存储器芯片采用8K×8位的芯片,RAM存储器芯片采用4K×8位的芯片, 试画出存储器与CPU的连接图。 (4)如果ROM存储器芯片采用16K×8位的芯片,RAM存储器芯片采用8K×8位的芯片,试画出存储器与CPU的连接图。

A.98.7%

B.99.3%

C.87%

D.90%

A.虚拟存储器是提高计算机运算速度的设备

B.虚拟存储器由RAM加上高速缓存组成

C.虚拟存储器的容量等于主存加上Cache的容量

D.虚拟存储器由物理内存和硬盘上的虚拟内存组成

高电平为读,低电平为写)。

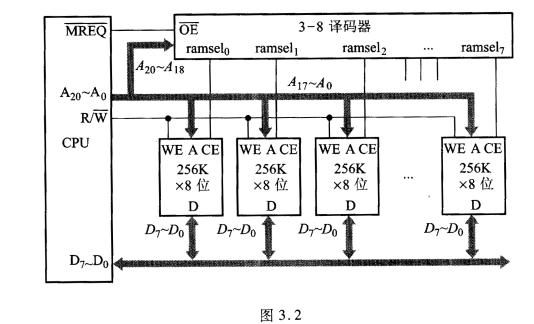

已知该机存储器地址空间从0连续编址,其地址空间分配如下:最低8K为系统程序区,由ROM芯片组成;紧接着40K为备用区,暂不连接芯片;而后78K为用户程序和数据空间,用静态RAM芯片组成;最后2K用于I/O设备(与主存统一编址)。现有芯片如下:

SRAM:16K×8位,其中CS:为片选信号,低电平有效,WE:为写控制信号,低电平写,高电平读。

ROM:8K×8位,其中CS:为片选信号,低电平有效,OE:为读出控制,低电平读出有效。

译码器:3―8译码器,输出低电平有效;为使能信号,低电平时译码器功能有效。

其它“与、或”等逻辑门电路自选。

(1)请问该主存需多少SRAM芯片?

(2)试画出主存芯片与CPU的连接逻辑图。

(3)写出各芯片地址分配表。

某CPU提供16条地址线(A0~A15),8条数据线(D0~D7)及R/ 控制信号,目前使用的存储器容量为8KB,其中4KB为ROM,采用2K×8位的芯片,其地址范围为0000H~0FFFH;4KB为DRAM,采用4K×2位芯片,其地址范围为4000H~4FFFH。问:

控制信号,目前使用的存储器容量为8KB,其中4KB为ROM,采用2K×8位的芯片,其地址范围为0000H~0FFFH;4KB为DRAM,采用4K×2位芯片,其地址范围为4000H~4FFFH。问:

(1)需ROM和DRAM芯片各多少片?

(2)画出CPU与存储器之间的连接图(译码器自定)。