题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

[主观题]

用集成3线—8线译码器74LS138和与非门设计一个全加器,设Ai为被加数,Bi为加数,低位进位为Ci-1,和为Si,向高位

用集成3线—8线译码器74LS138和与非门设计一个全加器,设Ai为被加数,Bi为加数,低位进位为Ci-1,和为Si,向高位进位为Ci。

查看答案

如果结果不匹配,请 联系老师 获取答案

如果结果不匹配,请 联系老师 获取答案

题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

用集成3线—8线译码器74LS138和与非门设计一个全加器,设Ai为被加数,Bi为加数,低位进位为Ci-1,和为Si,向高位进位为Ci。

如果结果不匹配,请 联系老师 获取答案

如果结果不匹配,请 联系老师 获取答案

更多“用集成3线—8线译码器74LS138和与非门设计一个全加器,…”相关的问题

更多“用集成3线—8线译码器74LS138和与非门设计一个全加器,…”相关的问题

用3线—8线译码器设计一个既能做一位二进制数的令加运算,又能做一位二进制数的伞减运算的电路。

要求:(1)根据题意要求,写真值表。

(2)写出电路输出函数的最简与或表达式。

(3)画出用3线—8线译码器74LS138芯片实现的电路。

试分别用下列方法设计全加器。

(1) 用与非门;

(2) 用或非门;

(3) 用双4选1数据选择器74LS153;

(4) 用3线-8线译码器74LS138和与非门。

A.00100000

B.11011111

C.11110111

D.00000100

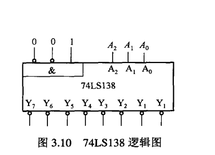

集成3-8译码器74LS138逻辑图如图3.10所示,要求用此3-8译码器和适当的逻辑门(规定与非门)设计一个全减器;设Ai为被减数,Bi为减数,低位向该位的借位为小差为Di向高位借位为Ji+1.

(1)列出全减器真值表;(2)写出函数逻辑表达式;(3)画出实现逻辑电路图.

用3线-8线译码器74HC138和门电路设计1位二进制全减器电路。输入为被减数、减数和来自低位的借位;输出为两数之差和向高位的借位信号。

A.000

B.010

C.101

D.111