题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

设计一个时序电路,它有两个输入X1和X0、一个输出Z0只有当X1;输入三个(或三个以上)1后,X0再输入一个1时,输出Z为1,而在同一时刻两个输入不同时为1,一旦Z=1,电路就回到原始状态。这里,X1输入三个1并不要求连续,只要其间没有X0=1插人即可。

如果结果不匹配,请 联系老师 获取答案

如果结果不匹配,请 联系老师 获取答案

题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

如果结果不匹配,请 联系老师 获取答案

如果结果不匹配,请 联系老师 获取答案

更多“设计一个时序电路,它有两个输入X1和X0、一个输出Z0只有当…”相关的问题

更多“设计一个时序电路,它有两个输入X1和X0、一个输出Z0只有当…”相关的问题

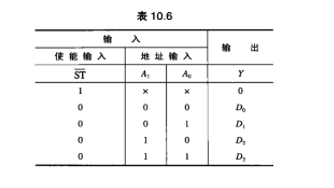

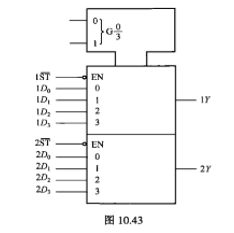

试用双4选1数据选择器74153和少量门设计一个有4个输入X3、X2、X1、X0和2个输出Y1、Y0的逻辑电路.电路输入为余3BCD码,输出为用2位二进制数表示的输入码中“1”的个数,例如,当输入X3X2X1X0=1010时,输出Y1Y0=10.当非余3码(伪码)输入时,要求输出Y1Y0=00.要求写出设计过程,画出电路图(规定X3、X2分别和数据选揮器地址码的高、低位相连接,74153的逻辑符号和功能表分别如图10.43和表10.6所示).

(13分)设将n(n,1)个整数存放到一维数组R中,试设计一个在时间和空间两方面尽可能有效的算法,将R中保有的序列循环左移P(0﹤P﹤n)个位置,即将R中的数据由(X0 X1 ……Xn-1)变换为(Xp Xp+1 ……Xn-1 X0 X1 ……Xp-1)要求: (1)给出算法的基本设计思想。 (2)根据设计思想,采用C或C++或JAVA语言表述算法,关键之处给出注释。 (3)说明你所设计算法的时间复杂度和空间复杂度

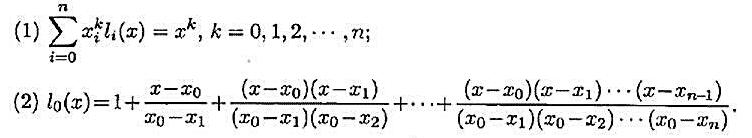

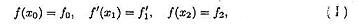

设x0=0,x2=1,x1∈(0,1),已知

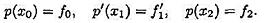

要求一个插值多项式p∈P2且满足

(1)当x1满足什么条件时,上述插值问题是适定的;

(2)当插值问题适定时,求出p(x);

(3)试对(2)中求出的p(x)进行误差分析。

将下述问题表示为混合整数规划模型:

min x0=f1(x1)+f2(x2).

其中

且满足下列约束条件:

(1)或者x1≥10,或者x2≥10;

(2)下列不等式至少有一个成立:

2x1+x2≥15,x1+x2≥15,x1+2x2≥15;

(3)|x1-x2|=0或5或10;

(4)x1≥0,x2≥0.

A.设计组合逻辑电路时建议使用阻塞赋值

B.设计时序电路时应尽量使用阻塞赋值方式

C.可以在两个或者两个以上的always过程中对同一变量赋值

D.对同一个变量可以既进行阻塞赋值,又进行非阻塞赋值

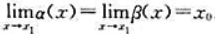

设a(x),β(x)在x1的某一去心邻域内满足:

(1)β(x)≠x0,a(x)≠β(x);

(2)存在常数M>0,使得β|(x)-x0|≤M|β(x)-a(x)|;

(3) .

.

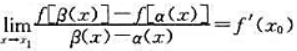

证明:若f(x)在x0可导,则

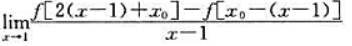

并求极限

题的基函数。试证明: