更多“试用中规模同步十进制加法计数器CT74160,并附加必要的门…”相关的问题

更多“试用中规模同步十进制加法计数器CT74160,并附加必要的门…”相关的问题

第2题

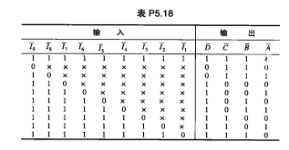

图P5.18是由二进制优先权编码器CT74LS147(真值表参见表P5.18)和同步十进制加法计数器CT74160

图P5.18是由二进制优先权编码器CT74LS147(真值表参见表P5.18)和同步十进制加法计数器CT74160组成的可控分频器.试说明当输入控制信号

分别为低电平,并假定CP脉冲的频率为f0时,由Z端输出的脉冲的频率是多少?

分别为低电平,并假定CP脉冲的频率为f0时,由Z端输出的脉冲的频率是多少?

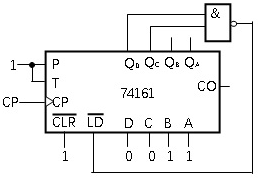

第3题

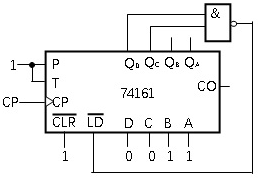

用4位二进制加法计数器74161构成的计数器电路如图所示,则对该计数器应用电路功能描述正确的是()。

A.余3码编码的十进制加法计数器

B.循环码编码的九进制加法计数器

C.余3码编码的三进制加法计数器

D.循环码编码的二进制加法计数器

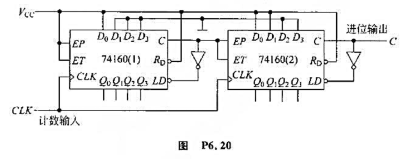

第6题

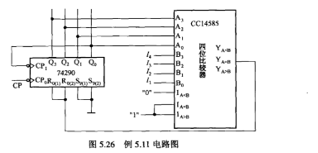

图5.26所示为一可变进制计数器,其模数受I4I3I2I1控制.其中,74290已通过将CP≇

图5.26所示为一可变进制计数器,其模数受I4I3I2I1控制.其中,74290已通过将CP1与Q0短接而连成8421BCD码十进制加法计数器的形式,CP0为外部计数输入端, 为异步置0端,

为异步置0端, 为异步置9端:CC14585为四位数码比较器,A3A2A1A0、B3B2B1B0为两个比较器的并行数据输入端,

为异步置9端:CC14585为四位数码比较器,A3A2A1A0、B3B2B1B0为两个比较器的并行数据输入端, 为扩展输入端,

为扩展输入端, 为比较输出端.

为比较输出端.

(1)分析I4I3I2I1=0110时,该电路为多少进制计数器,并画出其状态转换图.

(2)简述该可变进制计数器的工作原理.

第7题

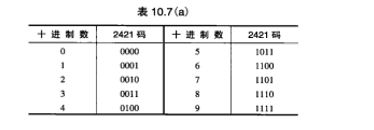

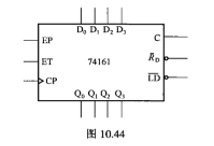

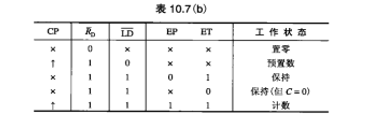

试用二进制同步计数器CT74161设计一个可控BCD码计数器.电路有一个控制端K,当K=0时,电路为8421B

CD码计数器;当K=1时,电路为2421BCD码计数器.规定设计电路采用反馈置数法.要求写出设计过程,画出电路图(2421BCD码见表10.7(a),CT74161逻辑符号和功能表见图10.44和表10.7(b)).

点击查看答案

如果结果不匹配,请

如果结果不匹配,请