题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

[主观题]

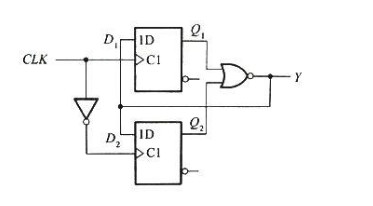

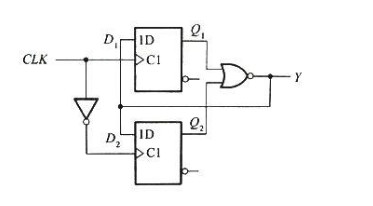

图5.23.1所示是用维持阻塞结构D触发器组成的脉冲分频电路。试画出在一系列CLK脉冲作用下输出端y对应的电压波

形。设触发器的初始状态均为Q=0。

查看答案

如果结果不匹配,请 联系老师 获取答案

如果结果不匹配,请 联系老师 获取答案

题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

形。设触发器的初始状态均为Q=0。

如果结果不匹配,请 联系老师 获取答案

如果结果不匹配,请 联系老师 获取答案

更多“图5.23.1所示是用维持阻塞结构D触发器组成的脉冲分频电路…”相关的问题

更多“图5.23.1所示是用维持阻塞结构D触发器组成的脉冲分频电路…”相关的问题

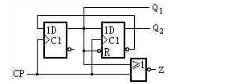

图题4.18所示是用CMOS边沿触发器和或非门组成的脉冲分配电路。试画出在一系列CP脉冲作用下Q1、Q2和Z端对应的输出电压波形。设触发器的初始状态为Q=0。

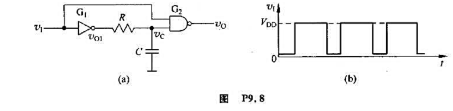

图P9.8(a)是用CMOS门电路和RC积分环节组成的积分型单稳态电路。试画出在图P9.8(b)所示输入脉冲作用下υ01、υ12和υ0的电压波形。假定触发脉冲的宽度大于输出脉冲的宽度。

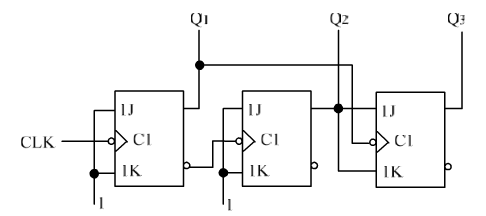

试画出图5.26.1所示电路在一系列CLK信号作用下Q1、Q2、Q3端输出电压的波形。触发器均为边沿触发方式,初始状态为Q=0。

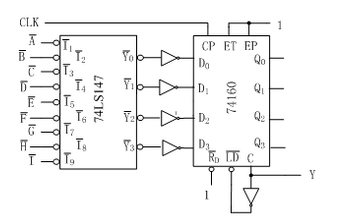

制信号A、B、C、D、E、F、G、H、I分别为低电平时由Y端输出的脉冲频率各为多少?已知CLK端的输入脉冲频率为10kHz。