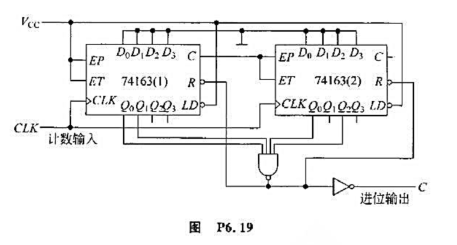

更多“图中所示为由两片同步十六进制计数器组成的计数器,试说明它的模…”相关的问题

更多“图中所示为由两片同步十六进制计数器组成的计数器,试说明它的模…”相关的问题

第4题

用两片74LS169构成模60计数器,要求计数器状态按两位8421BCD码的规律变化,即从0000 0000变到0101 1001。分别

用同步级联和异步级联的方式来构成这种计数器。画出连接图。

第5题

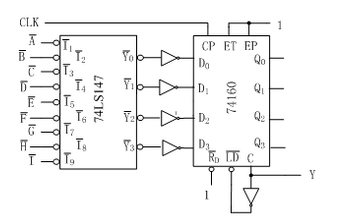

图6.24所示电路是用二一十进制优先编码器74LS147和同步十进制计数器74160组成的可控分频器,试说明当输入控

制信号A、B、C、D、E、F、G、H、I分别为低电平时由Y端输出的脉冲频率各为多少?已知CLK端的输入脉冲频率为10kHz。

第6题

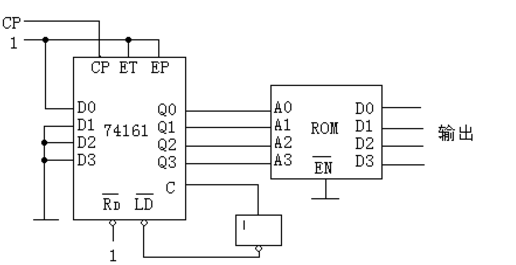

图是用16×4位ROM和同步十六进制加法计数器CT74161组成的脉冲分频器电路,ROM中的数据如表所示。试画出在CP信

号连续作用下D3、D2、D1、D0输出的电压波形,并说明它们和CP信号频率之比。

| 地址输入 | 数据输出 |

| A3A2A1A0 | D3D2D1D0 |

| 0 0 0 0 0 0 0 1 0 0 1 0 0 0 1 1 0 1 0 0 0 1 0 1 0 1 1 0 0 1 1 1 1 0 0 0 1 0 0 1 1 0 1 0 1 0 1 1 1 1 0 0 1 1 0 1 1 1 1 0 1 1 1 1 | 1 1 1 1 0 0 0 0 0 0 1 1 0 1 0 0 0 1 0 1 1 0 1 0 1 0 0 1 1 0 0 0 1 1 1 1 1 1 0 0 0 0 0 1 0 0 1 0 0 0 0 1 0 1 0 0 0 1 1 1 0 0 0 0 |

第9题

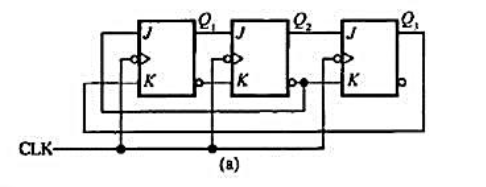

分析图3.16(a)所示同步计数电路,作出状态转移表和状态图.计数器是模几计数器?能否自启动?并画

分析图3.16(a)所示同步计数电路,作出状态转移表和状态图.计数器是模几计数器?能否自启动?并画出在时钟作用下的各触发器输出波形.

第10题

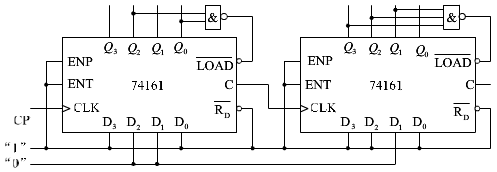

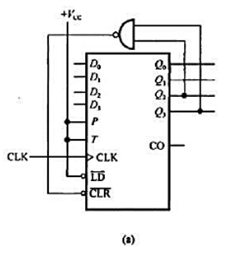

由同步二进制计数器74LS163构成的新模值的计数电路如图3.10(a)所示.分析电路实现模几计数,并画

由同步二进制计数器74LS163构成的新模值的计数电路如图3.10(a)所示.分析电路实现模几计数,并画出状态图.

第11题

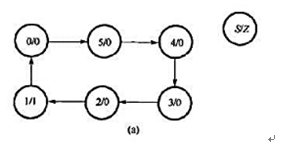

采用D触发器设计一个同步计数器,其计数状态转移图如图3.25(a)所示,画出逻辑电路图.

采用D触发器设计一个同步计数器,其计数状态转移图如图3.25(a)所示,画出逻辑电路图.

如果结果不匹配,请

如果结果不匹配,请